# DIGITAL LOGIC DESIGN AND ANALYSIS (DLDA)

#### NOVEMBER--2018

Q1 (a) Convert decimal number 576.24 into binary, base-9, octal, hexadecimal system.

(04)

Solution:

(i)Conversion to Binary

| 2 | 576 |   |

|---|-----|---|

| 2 | 288 | 0 |

| 2 | 144 | 0 |

| 2 | 72  | 0 |

| 2 | 36  | 0 |

| 2 | 18  | 0 |

| 2 | 9   | 0 |

| 2 | 4   | 1 |

| 2 | 2   | 0 |

| 2 | 1   | 0 |

|   | 0   | 1 |

The binary equivalent of 576 is 1001000000.

$$0.24 \times 2 = 0.48 \sim 0$$

$$0.48 \times 2 = 0.96 \sim 0$$

$$0.96 \times 2 = 1.92 \sim 1$$

$$0.92 \times 2 = 1.84 \sim 1$$

$$0.84 \times 2 = 1.68 \sim 1$$

$(576.24)_{10} = (1001000000.00111)_2$

(ii)Conversion to Base-9

| 9 | 576 |   |

|---|-----|---|

| 9 | 64  | 0 |

| 9 | 7   | 1 |

|   | 0   | 7 |

The base-9 equivalent of 576 is (710).

$$0.24 \times 9 = 2.16 \sim 2$$

$$0.16 \times 9 = 1.44 \sim 1$$

$$0.44 \times 9 = 3.96 \sim 3$$

$$0.96 \times 9 = 8.64 \sim 8$$

(576.24)10=(710.2138)9

## (iii)Conversion to Octal

| 8 | 576 |   |

|---|-----|---|

| 8 | 72  | 0 |

| 8 | 9   | 0 |

| 8 | 1   | 1 |

|   | 0   | 1 |

The octal equivalent of 576 is (1100).

$$0.24 \times 8 = 1.92 \sim 1$$

$$0.92 \times 8 = 7.36 \sim 7$$

$$0.36 \times 8 = 2.88 \sim 2$$

$$0.88 \times 8 = 7.04 \sim 7$$

$(576.24)_{10} = (1100.1727)_{8}$

#### (iv)Conversion to Hexadecimal

| 16 | 576 |   |

|----|-----|---|

| 16 | 36  | 0 |

| 16 | 2   | 4 |

|    | 0   | 2 |

The Hexadecimal equivalent of 576 is (240).

$$0.24 \times 16 = 3.84 \sim 3$$

$$0.84 \times 16 = 13.44 \sim D$$

$$0.44 \times 16 = 7.04 \sim 7$$

$$0.04 \times 16 = 0.64 \sim 0$$

$(576.24)_{10} = (240.3D70)_{16}$

.....

## (b) Construct hamming code for 1010 using odd parity.

(04)

Solution:

The given code is 1010 i.e. 4-bits.

∴ 3 Parity bits are required.

| 1  | 2  | 3 | 4  | 5 | 6 | 7 |

|----|----|---|----|---|---|---|

| P1 | P2 | 1 | P3 | 0 | 1 | 0 |

Using Odd - parity,

P1 = (3, 5, 7) = (1, 0, 0) = 0

P2 = (3, 6, 7) = (1, 1, 0) = 1

P3 = (5, 6, 7) = (0, 1, 0) = 0

: Hamming code is as follows:

| 1 | 2 | 3 | 4 | 5 | 6 | 7 |

|---|---|---|---|---|---|---|

| 0 | 1 | 1 | 0 | 0 | 1 | 0 |

The Hamming code for the given code is 1010 is 0110010.

\_\_\_\_\_\_

# (c)Convert (-89)₁₀ to its equivalent sign magnitude, 1's Complement and 2's Complement Form.

(04)

(04)

Solution:

The sign magnitude equivalent of (-89)<sub>10</sub> is as follows:

Sign bit

MSB magnitude

$(-89)_{10} = (11011001)_2$

The binary equivalent of  $(-89)_{10}$  is  $(11011001)_2$ . So, 1's complement of  $(-89)_{10}$  is  $(00100110)_2$

2's complement of (-89), is:

So, 2's complement of (-89)<sub>10</sub> is (00100111)<sub>2</sub>.

\_\_\_\_\_

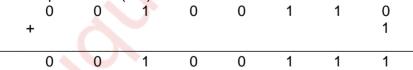

#### (d)Perform (BC5), - (A2B), without converting to any other base.

Solution:

Here, as 5 < B, so we borrow 16 from the previous value as the given values are in Hexadecimal format. 16 is then added to 5 ,thus it becomes 21 and 21 is subtracted from B. So, we get answer as A.

Since, we have borrowed from the previous value i.e C ,the value of C decreases by 1.So, it becomes B.

Thus,

$$(BC5)_H$$

-  $(A2B)_H$  =  $(19A)_H$

## (e) Prove De Morgan's theorem.

(04)

#### Solution:

The two theorems suggested by De-Morgan and which are extremely useful in Boolean algebra are stated as follows:

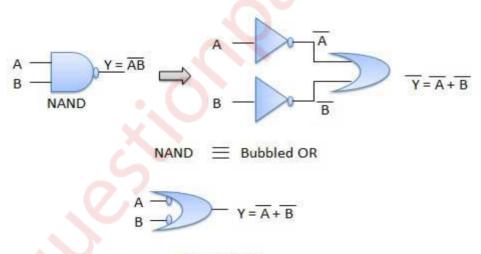

Theorem 1:

$$\overline{AB} = \overline{A} + \overline{B}$$

NAND = Bubbled OR:

This theorem states that the complement of a product is equal to the sum of individual complements.

This theorem can be verified using truth table as follows:

Bubbled OR

| A | В | AB | A | B |   |

|---|---|----|---|---|---|

| 0 | 0 | 1  | 1 | 1 | 1 |

| 0 | 1 | 1  | 1 | 0 | 1 |

| 1 | 0 | 1  | 0 | 1 | 1 |

| 1 | 1 | 0  | 0 | 0 | 0 |

Thus we can see that  $\overline{AB} = \overline{A} + \overline{B}$ .

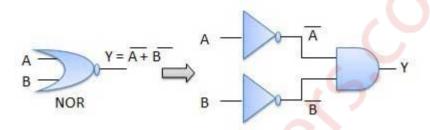

Theorem 2 :  $A + B = A \cdot B$

NOR = Bubbled AND:

This theorem states that the complement of a sum is equal to the product of individual complements.

NOR ≡ Bubbled AND

$$\Rightarrow A \xrightarrow{Y=A.B}$$

**Bubbled AND**

This theorem can be verified using truth table as follows:

| А | В | A + B | A | В | A·B |

|---|---|-------|---|---|-----|

| 0 | 0 | 1 ( ) | 1 | 1 | 1   |

| 0 | 1 | 0     | 1 | 0 | 0   |

| 1 | 0 | 0     | 0 | 1 | 0   |

| 1 | 1 | 0     | 0 | 0 | 0   |

Thus we can say that  $\overline{A + B} = \overline{A} \cdot \overline{B}$ .

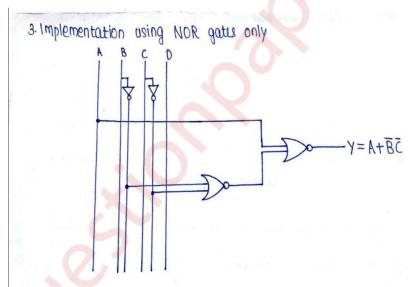

Q.2(a)Given the logic expression  $A + \overline{B} \ \overline{C} + A B \overline{D} + A B C D$

(10)

- 1. Express it in standard SOP form.

- 2. Draw K-map and simplify

- 3. Draw logic diagram using NOR gates only.

Solution:

The given expression is:

$$A + B C + A B D + A B C D$$

(i)Expressing the given expression in standard SOP form:

$$A + \overline{B} \overline{C} + A B \overline{D} + A B C D$$

$$\therefore$$

A (B +  $\overrightarrow{B}$ ) (C +  $\overrightarrow{C}$ ) (D +  $\overrightarrow{D}$ ) +  $\overrightarrow{B}$   $\overrightarrow{C}$  (A +  $\overrightarrow{A}$ ) (D +  $\overrightarrow{D}$ ) + A B  $\overrightarrow{D}$  (C +  $\overrightarrow{C}$ ) + A B C D

$$\therefore (A B + A B)(C D + \overline{C} D + \overline{C} D + \overline{C} D) + \overline{B} \overline{C} (A D + \overline{A} D + \overline{A} D + \overline{A} D) + \overline{A} \overline{B} \overline{C} D$$

$$+ \overline{A} \overline{B} \overline{C} D$$

$$\therefore$$

ABCD+ABCD+ABCD+ABCD+ABCD+ABCD+

The standard SOP form of the given expression is:

$$\ddot{A}$$

$\ddot{B}$   $\ddot{C}$   $\ddot{D}$  +  $\ddot{A}$   $\ddot{D}$   $\ddot{C}$   $\ddot{D}$   $\ddot$

$$ABC\overline{D} + ABCD$$

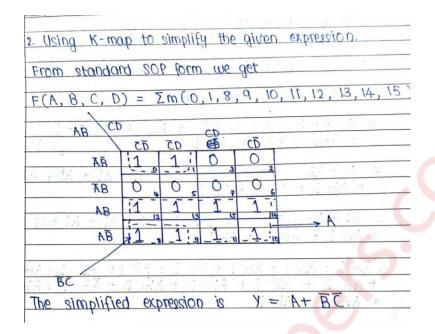

(ii)Using K-map to simplify the given expression :

From standard SOP form we get,

$$F(A, B, C, D) = \Sigma m (0, 1, 8, 9, 10, 11, 12, 13, 14, 15)$$

# Q.2(b)Reduce using Quine McCluskey method and realize the operation using only NAND gates. (10)

$F(A, B, C, D) = \pi M(0, 2, 3, 6, 7, 8, 9, 12, 13)$

Solution:

$F(A, B, C, D) = \pi M(0, 2, 3, 6, 7, 8, 9, 12, 13)$

$F(A, B, C, D) = \Sigma m (1, 4, 5, 10, 11, 14, 15)$

Step 1: Grouping the minterms according to the number of 1's

| Group | Minterm | A E | Binary represer | ntation<br>C | D |

|-------|---------|-----|-----------------|--------------|---|

| 1     | 1       | 0   | 0               | 0            | 1 |

|       | 4       | 0   | 1               | 0            | 0 |

| 2     | 5       | 0   | 1               | 0            | 1 |

|       | 10      | 1   | 0               | 1            | 0 |

| 3     | 11      | 1   | 0               | 1            | 1 |

|       | 14      | 1   | 1               | 1,5          | 0 |

| 4     | 15      | 1   | 1               | 1            | 1 |

Step 2: Grouping the minterms that form pairs

| Group | Minterm | Binary representation<br>A B | С | D |

|-------|---------|------------------------------|---|---|

| 1     | 1-5     | 0 -                          | 0 | 1 |

|       | 4-5     | 0 1                          | 0 | - |

| 2     | 10-11   | 1 0                          | 1 | - |

|       | 10-14   | 1                            | 1 | 0 |

| 3     | 11-15   | 1 -                          | 1 | 1 |

|       | 14-15   | 1                            | 1 | - |

Step 3: Grouping the minterms to form quad

| Group | Minterm         | Binary representation<br>A E | 3 | С | D |

|-------|-----------------|------------------------------|---|---|---|

| 1     | 10-11-14-<br>15 | 1 -                          |   | 1 | - |

| 9     | 10-14-11-<br>15 | 1 -                          | • | 1 | - |

# Step 4: Collecting all Prime Implicants

From Step 2, the prime implicants are  $\overline{A}$   $\overline{C}$  D and  $\overline{A}$  B  $\overline{C}$  . From Step 3, we get the prime implicants as A C.

$$F(A, B, C, D) = \overline{A} \overline{C} D + \overline{A} \overline{B} \overline{C} + A C$$

Step 5: Preparing the Prime Implicants Table

| Prime Implicant (PI) | Decimal numbers<br>(minterms) | Given Minterms    |

|----------------------|-------------------------------|-------------------|

|                      |                               | 1 4 5 10 11 14 15 |

| ĀCD                  | 1,5                           | x x               |

| ĀBC                  | 4,5                           | x x               |

| A C                  | 10,11,14,15                   | x x               |

$$\therefore F(A, B, C, D) = \overline{A} \overline{C} D + \overline{A} \overline{B} \overline{C} + \overline{A} C$$

# Q.3(a)Design a 4-bit binary to gray code converter.

(10)

Solution:

The truth table showing binary inputs being converted to gray outputs is as follows:

|    | BINARY INPL |    | 7   1 | GRAY CODE OUTPUT |     |    |    |  |

|----|-------------|----|-------|------------------|-----|----|----|--|

| В3 | B2          | B1 | В0    | G3               | G2  | G1 | G0 |  |

| 0  | 0           | 0  | 0     | 0                | 0   | 0  | 0  |  |

| 0  | 0           | 0  | 1     | 0                | 0   | 0  | 1  |  |

| 0  | 0           | 1  | 0     | 0                | 0   | 1  | 1  |  |

| 0  | 0           | 1  | 1     | 0                | 0   | 1  | 0  |  |

| 0  | 1           | 0  | 0     | 0                | 1_  | 1  | 0  |  |

| 0  | 1           | 0  | 1     | 0                | 0 1 |    | 1  |  |

| 0  | 1           | 1  | 0     | 0                | 1   | 0  | 1  |  |

| 0  | 1           | 1  | 1     | 0                | 1   | 0  | 0  |  |

| 1  | 0           | 0  | 0     | 1                | 1   | 0  | 0  |  |

| 1  | 0           | 0  | 1     | 1                | 1   | 0  | 1  |  |

| 1  | 0           | 1  | 0     | 1                | 1   | 1  | 1  |  |

| 1  | 0           | 1  | 1     | 1                | 1   | 1  | 0  |  |

| 1  | 1           | 0  | 0     | 1                | 0   | 1  | 0  |  |

| 1  | 1           | 0  | 1     | 1                | 0   | 1  | 1  |  |

| 1  | 1           | 1  | 0     | 1                | 0   | 0  | 1  |  |

| 1  | 1           | 1  | 1     | 1                | 0   | 0  | 0  |  |

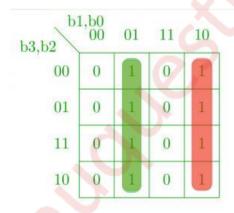

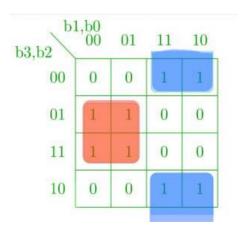

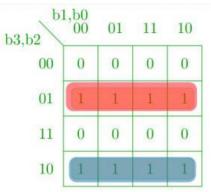

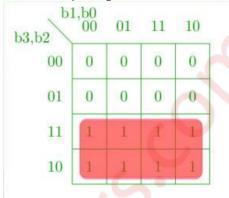

The K-maps for each gray output is as shown below.

# K-map for g₀:

∴

$$g_0 = b1 b0 + b1 b0$$

# K-map for g₁:

$$\therefore g_1 = \overline{b2} b3 + b2 \overline{b3}$$

## K-map for g<sub>2</sub>:

$$\therefore g_2 = \overline{b1} b2 + b1 \overline{b2}$$

# K-map for g<sub>3</sub>:

∴

$$g_3 = b3$$

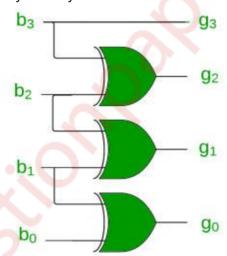

The logic diagram of 4-bit Binary to Gray code converter is as shown below.

\_\_\_\_\_

# Q.3(b)Design a 4 bit BCD adder using IC 7483 and necessary gates.

(10)

#### Solution:

- 1. A BCD adder adds two BCD digits and produces a BCD digit. BCD number cannot be greater than 9.

- 2. The two given BCD numbers are to be added using the rules of binary addition.

- 3. If sum is less than or equal to 9 and carry=0 then correction is necessary. The sum is correct and in the true BCD form.

- 4. But if sum is invalid BCD or carry=1, then the result is wrong and needs correction.

- 5. The wrong result can be corrected by adding six (0110) to it.

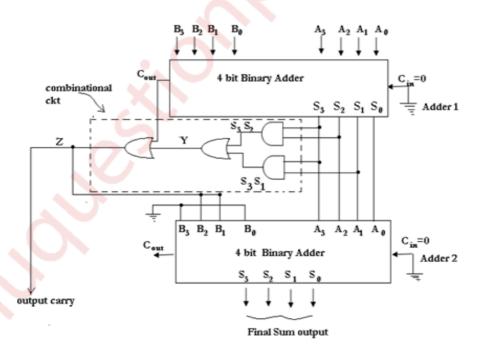

- 6. The 4 bit binary adder IC 7483 can be used to perform addition of BCD numbers.

- 7. In this, if the four-bit sum output is not a valid digit, or if a carry C3 is generated then decimal 6 (0110 binary) is to be added to the sum to get the correct result.

- 8. Fig1 shows a 1-digit BCD adders can be cascaded to add numbers several digits long by connecting the carry-out of a stage to the carry-in of the next stage.

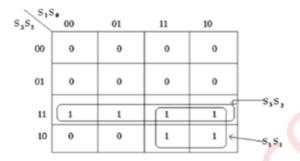

- 9. The output of combinational circuit should be 1 if the sum produced by adder 1 is greater than 9 i.e. 1001. The truth table is as follows:

|    | O/P |       |   |   |

|----|-----|-------|---|---|

| S3 | S2  | S2 S1 |   | Υ |

| 0  | 0   | 0     | 0 | 0 |

| 0  | 0   | 0     | 1 | 0 |

| 0  | 0   | 1     | 0 | 0 |

| 0  | 0   | 1     | 1 | 0 |

| 0  | 1   | 0     | 0 | 0 |

| 0  | 1   | 0     | 1 | 0 |

| 0  | 1   | 1     | 0 | 0 |

| 0  | 1   | 1     | 1 | 0 |

| 1  | 0   | 0     | 0 | 0 |

| 1  | 0   | 0     | 1 | 0 |

| 1  | 0   | 1     | 0 | 1 |

| 1  | 0   | 1     | 1 | 1 |

| 1  | 1   | 0     | 0 | 1 |

| 1  | 1   | 0     | 1 | 1 |

| 1  | 1   | 1     | 0 | 1 |

| 1  | 1   | 1     | 1 | 1 |

Truth table for BCD numbers

Y=1 since the sum obtained is an invalid BCD number.

K-map:

The Boolean expression is  $Y = S_3S_2 + S_3S_1$

- The BCD adder is shown below. The output of the combinational circuit should be 1 if Cout of adder-1 is high. Therefore Y is 0 with Cout of adder 1.

- The output of combinational circuit is connected to  $B_1B_2$  inputs of adder-2 and  $B_3 = B_1 + 0$  as they are connected to ground permanently. This makes  $B_3B_2B_1B_0 = 0110$  if Y' = 1.

- The sum outputs of adder-1 are applied to A<sub>3</sub>A<sub>4</sub>A<sub>6</sub> of adder-2. The output of combinational circuit is to be used as final output carry and the carry output of adder-2 is to be ignored.

#### BLOCK DIAGRAM OF BCD ADDER

4 bit BCD Adder

Fig5: 4-bit BCD adder

Operation of BCD Adder is as follows:

Case1: Sum  $\leq$  9 and carry = 0

• The output of combinational circuit Y' = 0. Hence  $B_3B_2B_1B_0 = 0.000$  for adder-2.

• Hence output of adder-2 is same as that of adder-2

## Case 2: Sum >9 and carry = 0

- If S3S2S1S0 of adder -1 is greater than 9, then output Y' of combinational circuits becomes 1.

- Therefore  $B_3B_2B_1B_0 = 0.1.1.0$  (of adder-2).

- Hence six (0 1 1 0) will be added to the sum output of adder-1.

- We get the corrected BCD result at the output of adder-2.

## Case 3: Sum ≤ 9 but carry = 1

- As carry output of addere-1 is high, Y' = 1.

- Therefore  $B_3B_2B_1B_0 = 0.1.1.0$  (of adder-2).

- Hence six (0 1 1 0) will be added to the sum output of adder-1.

- We get the corrected BCD result at the output of adder-2. Thus the Four bit BCD addition can be carried out using the binary adder.

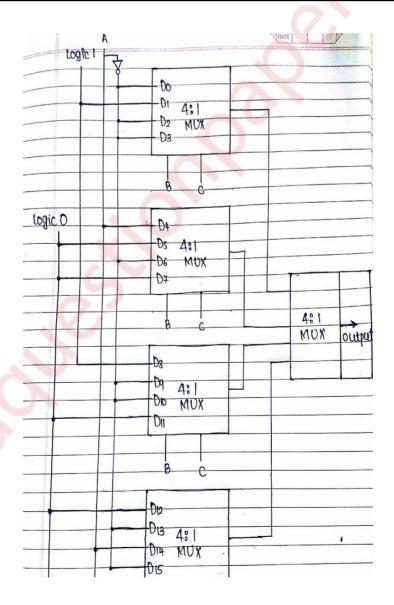

Q.4(a)Implement the following logic function using all 4 : 1 multiplexers with the select inputs as 'B', 'C', 'D', 'E' only.

$$F(A, B, C, D, E) = \Sigma(0,1,2,3,6,8,9,10,13,15,17,20,24,30)$$

(10)

#### Solution:

|   | D <sub>o</sub> | D₁ | D <sub>2</sub> | D₃ | D <sub>4</sub> | D₅ | D <sub>6</sub> | D <sub>7</sub> | D <sub>8</sub> | D <sub>9</sub> | <b>D</b> <sub>10</sub> | D <sub>11</sub> | D <sub>12</sub> | <b>D</b> <sub>13</sub> | <b>D</b> <sub>14</sub> | D <sub>15</sub> |

|---|----------------|----|----------------|----|----------------|----|----------------|----------------|----------------|----------------|------------------------|-----------------|-----------------|------------------------|------------------------|-----------------|

| Ā | 0              | 1  | 2              | 3  | 4              | 5  | 6              | 7              | 8              | 9              | 10                     | 11              | 12              | 13                     | 14                     | 15              |

| Α | 16             | 17 | 18             | 19 | 20             | 21 | 22             | 23             | 24             | 25             | 26                     | 27              | 28              | 29                     | 30                     | 31              |

|   | Ā              | 1  | Ā              | Ā  | Α              | 0  | Ā              | 0              | 1              | Ā              | Ā                      | 0               | 0               | Ā                      | Α                      | Ā               |

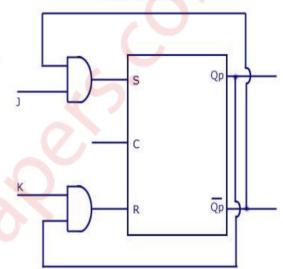

# Q.4(b)Convert a SR flip flop to JK flip flop.

(10)

Solution:

S-R Flip Flop to J-K Flip Flop

Conversion Table

| J-K | Inputs | Out | tputs | S-R Input |   |

|-----|--------|-----|-------|-----------|---|

| J   | K      | Qp  | Qp+1  | S         | R |

| 0   | 0      | 0   | 0     | 0         | X |

| 0   | 0      | 1   | 1     | X         | 0 |

| 0   | 1      | 0   | 0     | 0         | X |

| 0   | 1      | 1   | 0     | 0         | 1 |

| 1   | 0      | 0   | 1     | 1         | 0 |

| 1   | 0      | 1   | 1     | X         | 0 |

| 1   | 1      | 0   | 1     | 1         | 0 |

| 1   | 1      | 1   | 0     | 0         | 1 |

|   | 0 | 1 | 3 | 2 |

|---|---|---|---|---|

| C |   | Х | 0 | 0 |

|   | 4 | 5 | 7 | 6 |

| 1 |   | X | 0 | 1 |

K-Map

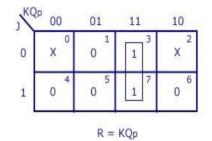

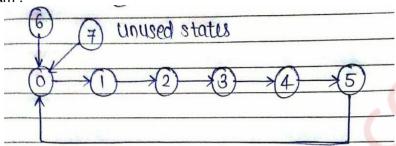

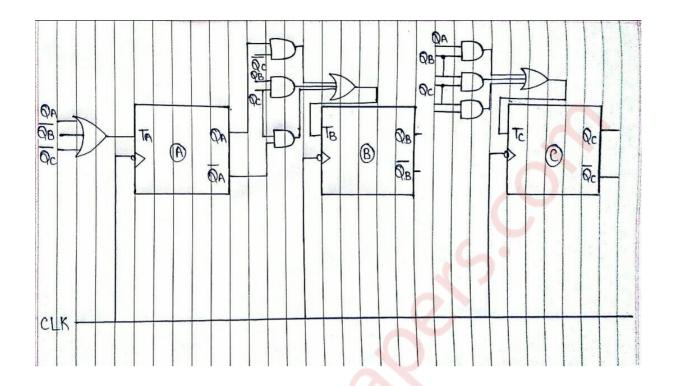

# Q.5(a)Design a mod-6 synchronous counter using T flip flop.

(10)

Solution:

(i)State Diagram:

# (ii)State Table:

| Present State |                |                | Next Stat        | е                       | 0                | Flip-flop inputs |    |    |

|---------------|----------------|----------------|------------------|-------------------------|------------------|------------------|----|----|

| Qc            | Q <sub>B</sub> | Q <sub>A</sub> | Q <sub>C+1</sub> | <b>Q</b> <sub>B+1</sub> | Q <sub>A+1</sub> | T.               | Тв | TA |

| 0             | 0              | 0              | 0                | 0                       | 1                | 0                | 0  | 1  |

| 0             | 0              | 1              | 0                | 1                       | 0                | 0                | 1  | 1  |

| 0             | 1              | 0              | 0                | 1                       | 1                | 0                | 0  | 1  |

| 0             | 1              | 1              | 1                | 0                       | 0                | 1                | 1  | 1  |

| 1             | 0              | 0              | 1                | 0                       | 1                | 0                | 1  | 1  |

| 1             | 0              | 1              | 0                | 0                       | 0                | 1                | 0  | 1  |

| 1             | 1              | 0              | 0                | 0                       | 0                | 1                | 1  | 0  |

| 1             | 1              | 1              | 0                | 0                       | 0                | 1                | 1  | 1  |

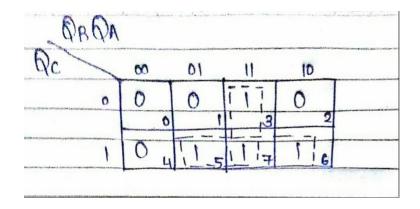

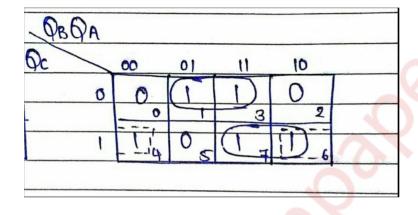

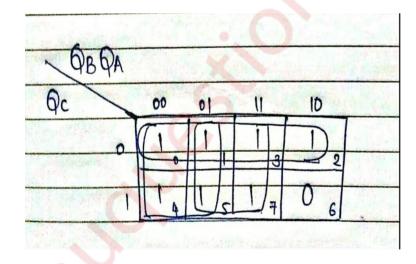

(iii)K map and simplification:

$T_c = Q_A Q_B + Q_B Q_C + Q_A Q_C$

$$T_B = Q_A \overline{Q_C} + Q_B Q_C + Q_C \overline{Q_A}$$

$$T_A = \overline{Q}_C + \overline{Q}_B + Q_A$$

(iv)Logic Diagram:

\_\_\_\_\_\_

## Q.5(b)Explain the operation of a 4-bit universal shift register.

(10)

#### Solution:

A shift register which can shift the data in only one direction is called as a unidirectional shift register. A shift register which can shift the data in both directions is called as bi-directional shift register. Similarly, a shift register which can shift data in both directions i.e shift left or right as well as load it parallelly, is called as a universal shift register.

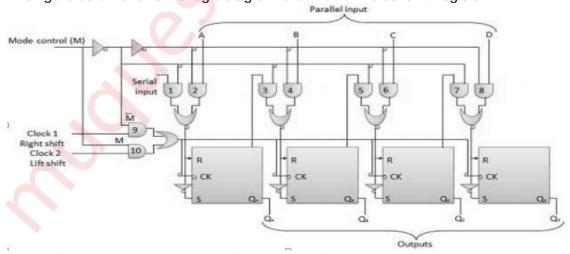

The figure below shows the logic diagram of a 4-bit universal shift register.

This shift register is capable of performing the following operations:

- 1.Parallel loading (parallel input parallel output)

- 2.Left shifting

### 3. Right shifting

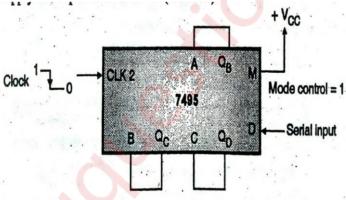

The mode control input is connected to Logic 1 for parallel loading operation whereas it is connected to 0 for serial shifting. When mode pin is connected to ground, the universal shift register acts as a bi-directional register. For serial left operation, the input is applied to serial input which goes into AND gate-1 of the above figure. For serial right operation, the serial input is applied to D input (input of AND gate-8). The well known example of universal shift register is in the form of IC 7495.

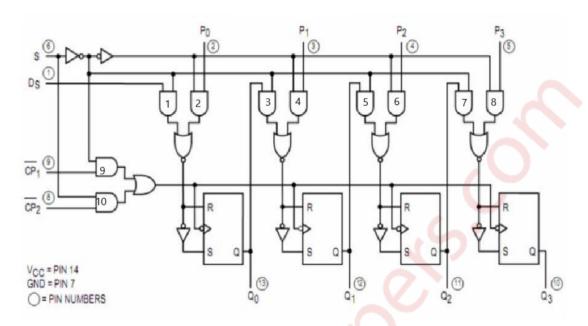

Universal Shift Register IC 7495:

It is a 4 bit shift register with serial and parallel synchronous operating modes. Because of its capability to operate in all possible modes, it is called a universal shift register. Some features of this chip are:

- 1. Synchronous shift left capacity.

- 2. Synchronous parallel loading is possible.

The figure below shows the pin configuration of IC 7495

- 3.It has separate clock inputs, one for shift operation and the other for load operation.

- 4. The cascading of two or more 7495 ICs for more than 4-bits is possible.

Outputs Clock 1 Clock 2 VCC QA QB QC QD R-Shift L-Shift 14 13 12 10 9 8 CK 1 Serial 7495 CK 2 Input Mode 3 5 1 2 4 6 В C Serial Α D Mode GND

A,B,C,D are the inputs to four internal flip flops with A acting as LSB and D as MSB. QA through QD are the corresponding outputs.

Inputs

Control

IC 7495 is capable of performing the following operations:

- 1. Parallel loading (parallel input parallel output)

- 2.Left shifting

- 3. Right shifting

Input

INTERNAL LOGIC DIAGRAM OF IC 7495

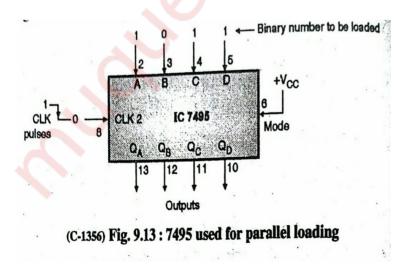

#### 1.Parallel loading:

The connection diagram for IC 7495 in parallel input parallel output mode is as shown in the figure below. The mode control (M) is connected to logic 1. This will enable the AND gates 2, 4, 6, 8 as shown in internal logic diagram. The AND gates 1, 3, 5, 7 are disabled. This allows data transfer from the inputs A, B, C, D to the flip flops and disable s the serial transfer of data. The 4-bit binary number which is to be loaded parallely is applied to the A, B, C, D inputs.

The clock applied at clock-2 input only will be paused through the flip flops because with M=1 and AND gate-10 is enabled and gate-9 is disabled. As soon as a falling edge of clock is applied, all flip-flops will change their status simultaneously and binary number applied to ABCD inputs will be loaded into the shift register. The unused inputs such as serial input and clock-1 can be left open or connected to ground because they are the don't care options for this mode.

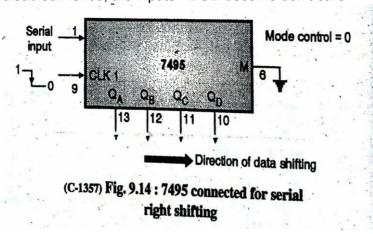

## 2. Serial Shift Right Operation:

The connection for serial shift right mode is as shown in the figure below. Make mode control = 0, therefore AND gates 1, 3, 5, 7 will be enabled and AND gate 2, 4, 6, 8 will get disabled. Hence, the inputs ABCD become don't care.

#### 3. Serial Shift Left Operation:

The connection diagram of 7495 for the shift left operation is as shown in the figure.  $Q_{\scriptscriptstyle D}$  is connected to C,  $Q_{\scriptscriptstyle C}$  to B and  $Q_{\scriptscriptstyle B}$  to A and the serial data is applied at input D.Mode control is connected to 1. Hence, the AND gates 2, 4, 6, 8 are enabled whereas 1, 3, 5, 7 are disabled. This will make the serial input (pin no. 1) a don't care input. The serial data is applied to D which will be routed through the enabled AND gates 2, 4, 6, 8 to facilitate the right shifting operation. As M = 1, AND gate - 10 is enabled and gate - 9 is disabled. So clock - 1 becomes a don't care input. Apply clock pulses to CLK - 2(shift left). Each high to low transition of clock will transfer data from D to  $Q_{\scriptscriptstyle D}$ ,  $Q_{\scriptscriptstyle D}$  to  $Q_{\scriptscriptstyle C}$ ,  $Q_{\scriptscriptstyle C}$  to  $Q_{\scriptscriptstyle B}$ ,  $Q_{\scriptscriptstyle B}$  to  $Q_{\scriptscriptstyle A}$ . Thus the shift left operation is performed.

(C-1358) Fig. 9.15: 7495 connected for serial shift left operation

# Q.6 Write Short notes on (any 2) (a)VHDL

(20)

#### Solution:

The long form of VHDL is Very High Speed Integrated Circuit (VHSIC) hardware description language.

VHDL is used to form a digital system at many levels of ideas ranging from algorithmic level to the gate level.

This language defines the syntax as well as simulation semantics for each language. It is a strong typed language which contains too many words to write.

VHDL is difficult to understand because it provides wide ranging of modelling capabilities but without learning the more complex features it is possible to incorporate a core subset of language which is simple and easy to understand.

Some Features of VHDL are:

- 1. Strongly typed language: Only LHS and RHS operators of the same type are allowed in VHDL.

- 2. Support hierarchies: Using VHDL, hierarchy can be represented. For example, full adder. In this case it is composed of half adder and OR gate.

- 3. VHDL supports for test and simulation of programs.

- 4. Concurrency: VHDL is a concurrent language which executes statements simultaneously in parallel.

- 5. VHDL supports different types of data modelling

- (i)Structural

- (ii)Data flow

- (iii)Behavioural

- (iv)Mixed

- 6. Supports sequential statement: VHDL can execute only one statement at a time in sequence only.

- 7. VHDL supports synchronous and asynchronous models.

- 8. VHDL can be used as a communication model between different CAD and CAE models.

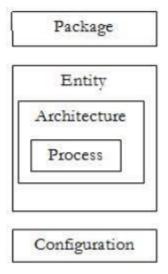

Structure of VHDL module:

Design units of VHDL code are independent components which are separately combined and stored in the library.

VHDL program is composed of the following design units:

- 1. Package (optional)

- 2. Entity

- 3. Architecture

- 4. Configuration (optional)

The diagram below shows the design units of VHDL.

#### Advantages of VHDL

- 1. VHDL allows designers to quickly develop designs requiring tens of thousands of logic gates.

- 2. VHDL supports multiple level of hierarchy and modular design methods.

- 3. VHDL allows user to pick any synthesis tool.

- 4. VHDL is multipurpose i.e. once calculation block is created then it can be used in many other projects.

- 5. For describing complex logic, VHDL provides powerful high level constructs.

#### Disadvantages of VHDL

VHDL is not a low level language i.e. gate level program. It is not suitable for verification of basic objects like gates. Because in VHDL these objects are readily available. Applications of VHDL

- 1. It is used in electronic design automation to describe mixed signal system such as FPGA (Field Programmable Gate Arrays) and Integrated circuits.

- 2. VHDL can be used as a general purpose parallel programming language.

- 3. VHDL can also be used for design and simulation purposes.

#### (b)TTL and CMOS logic families:

TTL family:

The long form of TTL is Transistor Transistor Logic. It is a logic family consisting completely of transistors. It employs transistors with multiple emitters. The digital ICs in the TTL family use only transistors as their basic building block. TTL ICs were first developed in 1965 and they were known as "Standard TTL". This version of TTL is not practically used now due to availability of advanced versions. Some characteristics of TTL family are as follows:

- 1. TTL is made up of BJTs (Bipolar Junction Transistor).

- 2. It has a high level noise margin of 0.4 V i.e.  $V_{NH} = 0.4 \text{ V}$ .

- 3. It has a low level noise margin of 0.4 V i.e.  $V_{NL} = 0.4 \text{ V}$ .

- 4. TTL family has less noise immunity than CMOS family.

- 5. The propagation delay of a standard TTL is 10nS.

- 6. It has a comparatively faster switching speed as compared to CMOS family.

- 7. It has a power dissipation of 10mW per gate i.e.  $P_D = 10$ mW.

- 8. TTL family has a speed power product of 100 pJ.

- 9. P<sub>o</sub> of TTL does not depend on frequency.

- 10. TTL has a Fan Out capacity of 10.

- 11. In TTL, inputs can remain floating. The floating inputs are treated as logic 1s.

- 12. Since BJTs require more space, TTLs have a comparatively low component density.

- 13. Transistors are operated in saturated or cut off regions.

- 14. Power supply voltage of TTL is fixed which is equal to 5V.

#### CMOS family:

Complementary Metal Oxide Semiconductor (CMOS) is a technology for constructing integrated circuits, employing MOSFET transistors. CMOS technology is used in microprocessors, microcontrollers, static RAM, and other digital logic circuits. CMOS technology is also used for several analog circuits such as image sensors (CMOS sensor), data converters, and highly integrated transceivers for many types of communication. Some characteristics of CMOS logic family are as follows:

- 1. CMOS devices are made up of N-channel MOSFET and P-channel MOSFET.

- 2. It has a high level noise margin of 1.45 V i.e.  $V_{NH} = 1.45 \text{ V}$ .

- 3. It has a low level noise margin of 1.45 V i.e.  $V_{NL} = 1.45 \text{ V}$ .

- 4. CMOS family has better noise immunity than TTL family.

- 5. The propagation delay of a metal gate CMOS is 105nS.

- 6. It has a comparatively slower switching speed as compared to TTL family.

- 7. It has a power dissipation of 0.1 mW per gate i.e. P<sub>o</sub>= 0.1 mW. Hence, it is used for battery backup applications.

- 8. CMOS family has a speed power product of 10.5 pJ.

- 9. P₀ of CMOS depends on frequency.

- 10. CMOS has a Fan Out capacity of 50.

- 11. The unused inputs should be returned to GND or V<sub>DD</sub>. They should never be left floating.

- 12. CMOS usually have a high component density than TTL as MOSFETs need less space while fabricating an IC.

- 13. MOSFETs are operated as switches i.e. in the ohmic region or cut off regions.

- 14. Power supply voltage of CMOS is flexible ranging from 3V to 15V.

#### (c)4-bit magnitude comparator

#### Solution:

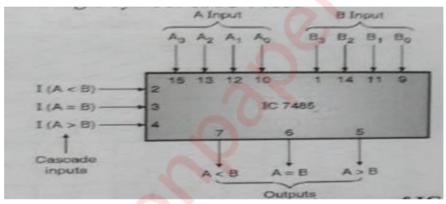

A 4-bit comparator is used to compare two 4-bit words A (A<sub>3</sub>- A<sub>0</sub>) and B (B<sub>3</sub>- B<sub>0</sub>). IC 7485 is a four bit comparator in the integrated circuit form. It is possible to cascade more than one IC 7485 to compare words of almost any size. The figure below shows the pin configuration and the logic symbol of IC 7485.

Fig13. Logic diagram of IC7485

The Pin names and their functions are as shown in the table below:

| Pin<br>name                      | Pin number  | Function                                                                                                              |

|----------------------------------|-------------|-----------------------------------------------------------------------------------------------------------------------|

| A <sub>o</sub> to A <sub>3</sub> | 10,12,13,15 | Binary input (opearand 1) Active high                                                                                 |

| B₀ to B₃                         | 9,11,14,1   | Binary input (opearand 2) Active high                                                                                 |

| I (A < B) I (A = B) I (A > B)    | 2<br>3<br>4 | These lines are used for cascading a number of IC 7485 outputs of the previous stage are fed as inputs to this stage. |

| A < B<br>A = B<br>A > B          | 7<br>6<br>5 | These are the outputs. When ICs 7485 are cascaded, these outputs are applied to cascading inputs of the next stage.   |

| Comparing inputs                                                                                               |                                                                                                      |                                                                                            |                                                                                  | Cascading inputs |                                                                                   |     | Outputs |                               |     |

|----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|------------------|-----------------------------------------------------------------------------------|-----|---------|-------------------------------|-----|

| A3,B3                                                                                                          | A2,B2                                                                                                | A1,B1                                                                                      | A0,B0                                                                            | A>B              | A <b< td=""><td>A=B</td><td>A&gt;B</td><td>A<b< td=""><td>A=B</td></b<></td></b<> | A=B | A>B     | A <b< td=""><td>A=B</td></b<> | A=B |

| A3>B3                                                                                                          | Х                                                                                                    | Х                                                                                          | Х                                                                                | Х                | Х                                                                                 | Х   | Н       | L()                           | L   |

| A3 <b3< td=""><td>Х</td><td>Х</td><td>X</td><td>Х</td><td>Х</td><td>Х</td><td>L</td><td>Ξ</td><td>L</td></b3<> | Х                                                                                                    | Х                                                                                          | X                                                                                | Х                | Х                                                                                 | Х   | L       | Ξ                             | L   |

| A3=B3                                                                                                          | A2>B2                                                                                                | Х                                                                                          | X                                                                                | Х                | Х                                                                                 | Х   | Н       | L                             | L   |

| A3=B3                                                                                                          | A2 <b2< td=""><td>Х</td><td>X</td><td>Х</td><td>Х</td><td>Х</td><td>C</td><td>Н</td><td>L</td></b2<> | Х                                                                                          | X                                                                                | Х                | Х                                                                                 | Х   | C       | Н                             | L   |

| A3=B3                                                                                                          | A2=B2                                                                                                | A1>B1                                                                                      | X                                                                                | Х                | Х                                                                                 | X   | Ξ       | L                             | L   |

| A3=B3                                                                                                          | A2=B2                                                                                                | A1 <b1< td=""><td>X</td><td>Х</td><td>X</td><td>X</td><td>L</td><td>Н</td><td>L</td></b1<> | X                                                                                | Х                | X                                                                                 | X   | L       | Н                             | L   |

| A3=B3                                                                                                          | A2=B2                                                                                                | A1=B1                                                                                      | A0>B0                                                                            | Х                | X                                                                                 | X   | Н       | L                             | L   |

| A3=B3                                                                                                          | A2=B2                                                                                                | A1=B1                                                                                      | A0 <b0< td=""><td>Х</td><td>X</td><td>X</td><td>L</td><td>Н</td><td>L</td></b0<> | Х                | X                                                                                 | X   | L       | Н                             | L   |

| A3=B3                                                                                                          | A2=B2                                                                                                | A1=B1                                                                                      | A0=B0                                                                            | H                | V                                                                                 | L   | Н       | L                             | L   |

| A3=B3                                                                                                          | A2=B2                                                                                                | A1=B1                                                                                      | A0=B0                                                                            |                  | Η                                                                                 | L   | L       | Н                             | L   |

| A3=B3                                                                                                          | A2=B2                                                                                                | A1=B1                                                                                      | A0=B0                                                                            | ٦                | L                                                                                 | Н   | L       | L                             | Н   |

| A3=B3                                                                                                          | A2=B2                                                                                                | A1=B1                                                                                      | A0=B0                                                                            | X                | Х                                                                                 | Н   | L       | L                             | Н   |

| A3=B3                                                                                                          | A2=B2                                                                                                | A1=B1                                                                                      | A0=B0                                                                            | Н                | Н                                                                                 | L   | L       | L                             | L   |

| A3=B3                                                                                                          | A2=B2                                                                                                | A1=B1                                                                                      | A0=B0                                                                            | L                | L                                                                                 | L   | Н       | Н                             | L   |