## Paper / Subject Code: 51222 / Electronics Devices and Circuits

June 6, 2024 02:30 pm - 05:30 pm 1T01033 - S.E.(Electronics and Telecommunication ) (SEM-III)(Choice Base Credit Grading System ) (R- 19) (C Scheme) / 51222 - Electronics Devices and Circuits QP CODE: 10057487

Time: 3 hour Max. Marks: 80

\_\_\_\_\_

Q1 is compulsory.

Attempt any three from Q2 to Q6.

## Q1 Solve any Four

5 marks each

- A Explain the operation of a semiconductor pn junction diode with the help of VI characteristics.

- B Explain Miller's capacitance theorem.

- C What is the effect of coupling and bypass capacitors on the frequency response of a single stage amplifier?

- D What is crossover distortion in Class B power amplifiers?

- E Explain the working of a two transistor constant current source using E-MOSFET

Q2 10 marks each

- A Draw the voltage divider biasing circuit for JFET and derive the quiescent point  $(V_{DSQ},I_{DQ})$  equations.

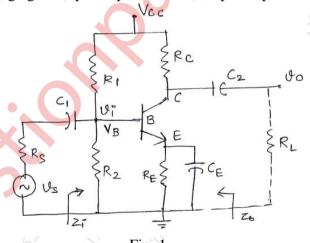

- B Draw a small signal equivalent circuit of the given circuit in fig. 1 and derive the expression for voltage gain, input impedance and output impedance.

Fig. 1

Q3

A For a Class B amplifier providing a 20 V peak signal to a 16  $\Omega$  load (speaker) and a

A For a Class B amplifier providing a 20 V peak signal to a 16  $\Omega$  load (speaker) and a power supply of  $V_{CC} = 30$  V, determine the input power, output power and circuit efficiency.

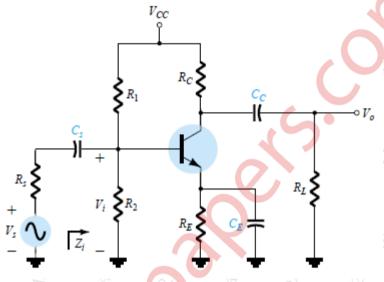

B Calculate low cutoff frequencies due to coupling and bypass capacitors of the circuit given in fig. 2

Fig. 2

$$C_s = 10 \ \mu\text{F},$$

$C_E = 20 \ \mu\text{F},$   $C_C = 1 \ \mu\text{F}$   $R_s = 1 \ \text{k}\Omega,$   $R_1 = 40 \ \text{k}\Omega,$   $R_2 = 10 \ \text{k}\Omega,$   $R_E = 2 \ \text{k}\Omega,$   $R_C = 4 \ \text{k}\Omega,$   $R_L = 2.2 \ \text{k}\Omega$   $R_C = 4 \ \text{k}\Omega,$   $R_C = 4$

Q4 10 Marks each

A Draw and explain high frequency model for BJT in CE configuration.

B Draw and explain a series fed class A power amplifier with the help of neat diagram and waveforms and derive the expression of power efficiency.

10 Marks each **Q5** A

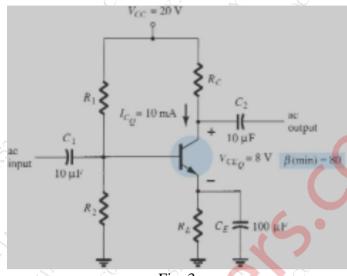

Design a voltage divider bias circuit to operate at the given conditions. Refer Fig. 3

Fig. 3

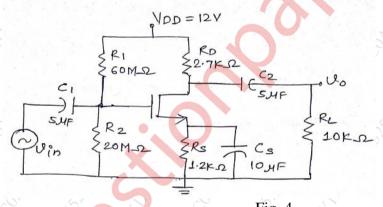

Determine the input impedance, output impedance and voltage gain for the given В circuit. Refer fig. 4

Fig. 4

$$V_{GSQ} = 1.872 \text{ V}, I_{DSQ} = 0.94 \text{ mA}$$

**Q6** 10 Marks each

Derive the equation of CMRR for the MOS differential pair amplifier.

Explain the operation of a MOS differential amplifier with differential mode input signal.

57487